Chipbonden und Ausrüstung

Bei Cicor in Radeberg ist das Chipbonden ein wichtiger Prozess zur Montage von Chips auf Oberflächen mit unterschiedlichen Eigenschaften. Dabei kann ein breites Spektrum an Die-Größen und -Stärken sowie unterschiedliche Materialien, Oberflächen-beschaffenheiten und Lieferformen verarbeitet werden. Das Chipbonden kann entweder manuell oder vollautomatisch auf einem Chip-Bonder durchgeführt werden.

Der Anlagenpark von Chip-Bondern bei Cicor in Radeberg ist in den letzten Jahren weiter aufgebaut worden. Spezielle Anforderungen haben im Laufe der Jahre zur Anschaffung und zum Einsatz von manuellen, halb-automatischen und automatischen Chip-Bondern geführt. Die automatischen Chip-Bonder werden hauptsächlich in Reinräumen der Klassen ISO5 und ISO7 eingesetzt, abhängig von den Anforderungen an die Sauberkeit der zu bearbeitenden Produkte. Sie werden u.a. für das Handling spezieller Chips in der Serienfertigung (sehr dünne Chips <30 µm Dicke oder kleine Chips bis 0,1-0,15 µm Kantenlänge) eingesetzt.

Wichtig sind neben einer guten Bestück-genauigkeit (Cmk mit bis zu ±7 µm@3s) auch stabile Pick & Place-Prozesse, Montage direkt vom Wafer oder vorsortiert aus Wafflepacks, eine automatische optische Erkennung und vieles mehr.

Neben den automatischen Chip-Bondern verfügt Cicor auch über manuelle Chip-Bonder zur hochgenauen Positionierung optischer Chips oder Fibre Optic Panels (FOPs) für Kleinserienfertigungen. Mit diesen manuellen Bondern können bessere Bestückgenauigkeiten bis ±3µm@3s realisiert werden.

Qualitätsprüfungen bei der Chip-Montage

Mechanische, optische und radiografische Prüfungen (Röntgen) werden zur Qualitätskontrolle von bestückten Baugruppen prozessbegleitend durchgeführt. Diese Tests und Prüfungen basieren auf allgemeinen Standards wie MIL-STD883, ESCC/ECSS-Raumfahrtspezifikationen oder auch auf verschiedensten Kundenspezifikationen mit individuellen Anforderungen. Wichtige Qualitätskriterien für Chipbondverbindungen sind z.B. mechanische Scherfestigkeiten, optische Kriterien wie Klebstoff- oder Lot-Benetzung, Verunreinigungen von Oberflächen sowie die Positioniergenauigkeit von Chips und bei gelöteten Verbindungen der Anteil von Fehlstellen in Lötverbindungen.

Verbindungstechnologien in der Chipmontage

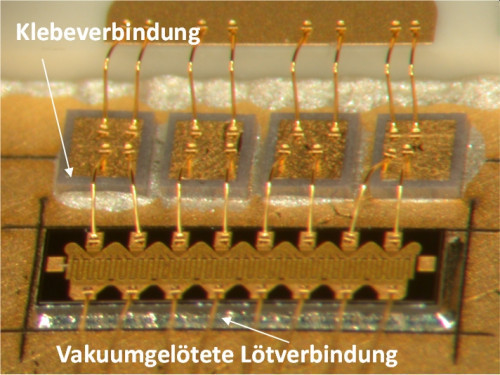

Abb. 1 Chipbonden: Löten und KlebenBei Cicor stehen drei Technologien für die Montage von Chips auf Verdrahtungsträgern wie Keramiksubstraten, auf PCBs oder in Gehäusen zur Verfügung. Nach der Art der Verbindungstechnologie werden sie in Kleben, Löten und Sintern unterschieden. Zum Einsatz kommen dafür Verbindungsmaterialien wie Klebstoffe, Lote und Sinterpasten.

Abb. 1 Chipbonden: Löten und KlebenBei Cicor stehen drei Technologien für die Montage von Chips auf Verdrahtungsträgern wie Keramiksubstraten, auf PCBs oder in Gehäusen zur Verfügung. Nach der Art der Verbindungstechnologie werden sie in Kleben, Löten und Sintern unterschieden. Zum Einsatz kommen dafür Verbindungsmaterialien wie Klebstoffe, Lote und Sinterpasten.

a) Klebeverbindungen

Für Klebeverbindungen werden je nach Produkt- und Kundenanforderung verschiedene Klebstofftypen eingesetzt. Diese lassen sich grob unterschieden in elektrisch leitfähig oder nicht leitfähig, thermisch leitfähig, gefüllt oder ungefüllt, 1K oder 2K, sowie nach der Art des Aushärtungs-mechanismus. Da die Klebstoffe hauptsächlich in Form von Pasten verfügbar sind, kann der Auftrag, je nach Viskosität und Eigenschaften, mit verschiedenen Verfahren wie Dispensen, Stempeln oder dem Siebdruck erfolgen.

Um gute Ergebnisse beim Klebeprozess zu erreichen, muss die Menge und Verteilung des verwendeten Klebstoffs während der Montage passend eingestellt werden, unter Beachtung von Eigenschaften wie Klebstoffviskosität, Chipgröße, Chip-Seitenverhältnisse und dem Benetzungsverhalten der Oberflächen.

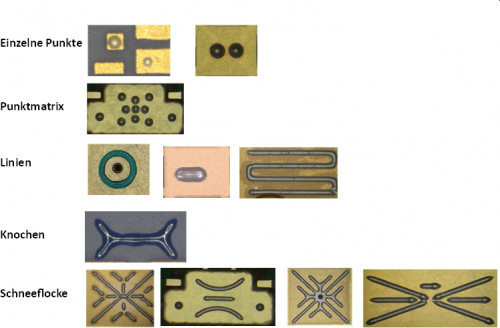

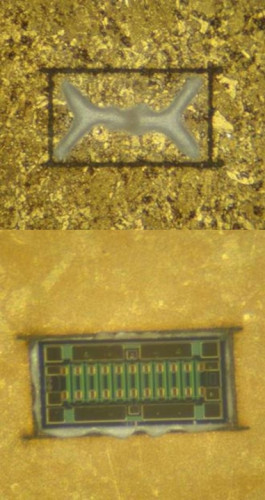

Für ein gutes Klebeergebnis ist es notwendig, an das jeweilige Chip und Substrat angepasste Auftragsmuster für das Auftragen von Klebstoffen zu verwenden (siehe Abb. 2). Für kleine Chips werden aufgrund der geringen benötigten Klebstoffmenge meist nur einzelne Punkte oder eine kleine Punktmatrix verwendet. Bei größeren Chips mit variierenden Seitenverhältnissen müssen andere Muster wie Linien, Knochen oder Schneeflocken verwendet werden, um in vertretbarer Zeit eine ausreichende Menge Klebstoff zu applizieren sowie eine gute Klebstoffverteilung unter den Chips und ein gutes Benetzungsergebnis zu erreichen. Die Dosierergebnisse hängen wesentlich auch von der Art und Größe der verwendeten Dosiernadel und von Prozess-parametern wie Druck/Zeit, Verfahr-geschwindigkeit oder vordefiniertem Volumen ab.

Nach dem Auftrag des Klebstoffs und dem Bestücken der Chips ist es notwendig den Klebstoff auszuhärten.

Abb. 2: Unterschiedliche Muster des Klebstoffauftragens abhängig von den AnforderungenJe nach den Anforderungen der Materialien/ Produkte und ihrer Konstruktion kommen verschiedene Klebstoffe mit unterschiedlichen Aushärtungsmechanismen wie Temperatur, UV-Licht, Eigenvernetzung oder Feuchtigkeit zum Einsatz. Typische Aushärtetemperaturen für Epoxidharzklebestoffe liegen z.B. im Bereich von Raumtemperatur bis zu 150°C.

Abb. 2: Unterschiedliche Muster des Klebstoffauftragens abhängig von den AnforderungenJe nach den Anforderungen der Materialien/ Produkte und ihrer Konstruktion kommen verschiedene Klebstoffe mit unterschiedlichen Aushärtungsmechanismen wie Temperatur, UV-Licht, Eigenvernetzung oder Feuchtigkeit zum Einsatz. Typische Aushärtetemperaturen für Epoxidharzklebestoffe liegen z.B. im Bereich von Raumtemperatur bis zu 150°C.

b) Vakuumgelötete Lötverbindungen

Eine weitere Methode der Chipmontage ist das Vakuumlöten. Dieses Lötverfahren ist bekannt für seine gute Sauberkeit, da kein Flussmittel im Lot verwendet wird im Gegensatz zum Standard-Reflow-Verfahren mit Lotpaste. Die Sauberkeit der Chipoberflächen, ohne zusätzliche erforderliche Reinigungsschritte, ist z.B. für Produkte der Luft- und Raumfahrt, eine wesentliche Voraussetzung für eine gute Verarbeitbarkeit der montierten Chips bei nachfolgenden Prozessen wie z.B. dem Drahtbonden.

Das Lotmaterial wird meist in Form von Lotpreforms (vorgeschnittene Metallfolie), vorapplizierten umgeschmolzenen und gereinigten Lotdepots oder als aufgedampfte Lotschichten aufgetragen. Zum Einsatz kommen beim Vakuumlöten hauptsächlich Lotlegierungen wie z.B. AuSn, SnAgCu, SnIn, SnBi oder auch PbSn Lote für Luft- und Raumfahrt.

Viele Arten keramischer und metallischer Werkstoffe sind für das Vakuumlöten geeignet, da sie temperaturbeständig und ausgasungsarm sind. Kunststoffe werden, je nach Temperaturbelastung beim Löten, möglichst nicht verwendet, da sie den Vakuumprozess durch Ausgasungseffekte verunreinigen können.

Die korrekte Positionierung der Chips während des Lötens wird durch den Einsatz von Lötbarrieren wie mechanischen Stufen, gefrästen oder gelaserten Linien sichergestellt.

Typische Aufschmelztemperaturen der Lote liegen je nach Lotlegierung im Bereich von 130°C bis 290°C. Mögliche Löttemperaturen von bis zu 400°C bei geringen Kammerdrücken von bis zu 0,1mBar können in einem Vakuumlötofen realisiert werden.

Abb. 3 Vollautomatische Batch-VakuumlötanlageEine vollautomatische Batch-Vakuumlötanlage mit zwei Lötöfen und Roboterhandling ist in Abb. 3 dargestellt. Der Roboter übernimmt den Werkstückträger mit dem Lötgut an der Ladeposition der Transportstrecke und bewegt ihn von der Ladeposition direkt in die Vakuumlötkammer. Der Transport der Werkstückträger muss sehr genau abgestimmt erfolgen und frei von Vibrationen oder Stößen sein, um eine unkontrollierte Bewegung oder Versatz der zu lötenden Komponenten zu vermeiden, da diese nur lose aufeinandergestapelt werden. Der Vakuumlötprozess startet automatisch, sobald die Kammer geschlossen ist. Nach dem Löten erfolgt der Entladevorgang auf die gleiche Weise.

Abb. 3 Vollautomatische Batch-VakuumlötanlageEine vollautomatische Batch-Vakuumlötanlage mit zwei Lötöfen und Roboterhandling ist in Abb. 3 dargestellt. Der Roboter übernimmt den Werkstückträger mit dem Lötgut an der Ladeposition der Transportstrecke und bewegt ihn von der Ladeposition direkt in die Vakuumlötkammer. Der Transport der Werkstückträger muss sehr genau abgestimmt erfolgen und frei von Vibrationen oder Stößen sein, um eine unkontrollierte Bewegung oder Versatz der zu lötenden Komponenten zu vermeiden, da diese nur lose aufeinandergestapelt werden. Der Vakuumlötprozess startet automatisch, sobald die Kammer geschlossen ist. Nach dem Löten erfolgt der Entladevorgang auf die gleiche Weise.

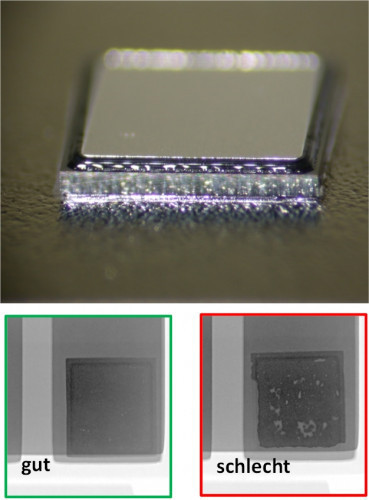

Die Qualität der vakuumgelöteten Lötverbindungen wird bei jedem Produktionsauftrag durch eine eigene Röntgeninspektion überprüft. Der Anteil von Fehlstellen im Lot, die Benetzung des Lotes sowie die Positionierung der Chips sind wichtige Qualitätskriterien, die anhand der Röntgenbilder beurteilt werden. Die Lötergebnisse werden maßgeblich von der Prozessführung, dem Lötprofil, der Sauberkeit und Qualität der verwendeten Materialien und Lote sowie der Sauberkeit der Prozesskammer und der Atmosphäre während der Verarbeitung beeinflusst. Die zulässigen Grenzwerte für den Gehalt von Fehlstellen und die Benetzung sind beim Löten von Chips entweder durch die MIL STD 883 definiert oder basieren auf individuellen Kundenvereinbarungen. Einfache Beispiele für gute und schlechte Lötergebnisse hinsichtlich Lotbenetzung und Fehlstellenanteil im Röntgenbild sind in Abb. 4 dargestellt.

Der Vakuumlötprozess selbst erfolgt in mehreren Schritten. Zum Einsatz kommen Sattelprofile wie beim Standard Reflowlöten. Nach dem Prozessstart wird das Lötgut auf eine Temperatur unterhalb vom Schmelzpunkt des Lotes erwärmt und über eine bestimmte Zeit für mehrere Minuten konstant gehalten. In diesem Sattel-Bereich wird das Lötgut gleichmäßig durchwärmt.

Abb. 4. LötergebnisseDie Prozessaktivierung bzw. Reduktion potentiell vorhandener Oxide auf den Oberflächen erfolgt durch den Einsatz von Aktivierungsgasen wie Formiergas (N2H2), Ameisensäure (HCOOH) oder reinem Wasserstoff (H2), welche in einer Abfolge von Spülprozessen eingesetzt werden. Außerdem wird der Restsauerstoff aus der Kammer entfernt und mittels Vakuum die Rückstände von Ausgasungen der Materialien so gut wie möglich entfernt. Anschließend wird das Lötgut weiter erwärmt und bei Erreichen der Schmelztemperatur des Lotes in der Peakzone vom Lötprofil, beginnt das Lot zu fließen und benetzt die Metalloberflächen des Substrates und der Chiprückseite. Unterstützt wird dieser Vorgang durch den weiteren Einsatz der Aktivierungsgase, die den Benetzungsvorgang fördern. Zum Schluss wird die Kammer wiederholt unter Vakuum gesetzt, um eventuell vorhandene Gasblasen zu entfernen, die im geschmolzenen Lot durch Lufteinschlüsse oder Ausgasungen der Materialien entstehen können.

Abb. 4. LötergebnisseDie Prozessaktivierung bzw. Reduktion potentiell vorhandener Oxide auf den Oberflächen erfolgt durch den Einsatz von Aktivierungsgasen wie Formiergas (N2H2), Ameisensäure (HCOOH) oder reinem Wasserstoff (H2), welche in einer Abfolge von Spülprozessen eingesetzt werden. Außerdem wird der Restsauerstoff aus der Kammer entfernt und mittels Vakuum die Rückstände von Ausgasungen der Materialien so gut wie möglich entfernt. Anschließend wird das Lötgut weiter erwärmt und bei Erreichen der Schmelztemperatur des Lotes in der Peakzone vom Lötprofil, beginnt das Lot zu fließen und benetzt die Metalloberflächen des Substrates und der Chiprückseite. Unterstützt wird dieser Vorgang durch den weiteren Einsatz der Aktivierungsgase, die den Benetzungsvorgang fördern. Zum Schluss wird die Kammer wiederholt unter Vakuum gesetzt, um eventuell vorhandene Gasblasen zu entfernen, die im geschmolzenen Lot durch Lufteinschlüsse oder Ausgasungen der Materialien entstehen können.

Vakuumgelötete Verbindungen von Chip-Baugruppen bieten mehrere Vorteile im Vergleich zur Verwendung von elektrisch leitfähigen Klebstoffen als Verbindungs-material. Eine erhöhte Wärmeleitfähigkeit (bis zu 60-70W/mK), bessere Zuverlässigkeit, hohe Sauberkeit und ein geringes Ausgasungs-verhalten, sind einige der wichtigsten Vorteile und machen das Vakuumlöten besonders für Anwendungen in hermetischen Gehäusen interessant. Daher wird dieses Chipbond-verfahren bevorzugt in der Luft- und Raumfahrt sowie für industrielle High-Power-Anwendungen eingesetzt.

c) Sintern

Eine weitere Methode zur Montage von Chips ist das Silbersintern. Man unterscheidet generell zwischen der Verwendung von Sinterpasten oder vorgefertigten Sinterfolien sowie zwischen dem Sintern mit oder ohne Druck. Bei Cicor in Radeberg werden hauptsächlich Sinterpasten für das drucklose Sintern im Montageprozess verwendet. Dieser Prozess ist beim Auftrag der Pasten mittels Dispensen, über die Bestückung der Chips und den anschließenden Sinterprozess in einem Batchofen (Sintertemperaturen liegen im Bereich von 175°C – 200°C) vergleichbar zum Montageprozess mit Klebstoffen und kann recht einfach realisiert werden. Gegenüber elektrisch leitfähigen Klebstoffen zeichnen sich diese Sinterpasten durch eine höhere Zuverlässigkeit und eine deutlich bessere Wärmeleitfähigkeit von bis zu 140W/mK aus und sind deswegen besonders für High-Power-Anwendungen geeignet.

Abb.5. Beispiel für SinterprozessVerarbeitung ultradünner Chips

Abb.5. Beispiel für SinterprozessVerarbeitung ultradünner Chips

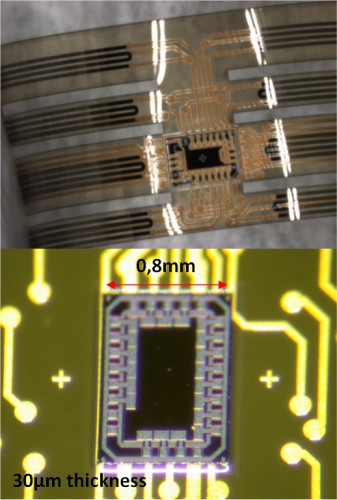

Ultradünne Chips mit geringen Dicken von minimal 20µm werden bevorzugt für Anwendungen eingesetzt, bei denen Platzersparnis eine wichtige Anforderung ist (z. B. für medizinische Anwendungen). Die Montage ultradünner Chips ist ein anspruchsvolles Gebiet der Chipbond-technologie, da diese Chips sehr empfindlich hinsichtlich Beschädigungen sind. Kritisch ist der Pick-up-Prozess vom Wafer, das Handling in der Anlage bis hin zum Absetzen auf dem Substrat. Die Verwölbung dünner Chips ist ein wichtiger Parameter, welcher während des Bestückprozesses und der Klebstoffaushärtung im Ofen zwingend kontrolliert werden muss, um gleichmäßige gute Ergebnisse zu erzielen. Es werden bei Cicor speziell angepasste, niedrigviskose, elektrisch nichtleitende Klebstoffe verwendet. Wichtig ist es eine gute Benetzung des Klebstoffs am Chip zu gewährleisten und gleichzeitig das Risiko einer Verunreinigung der Chipoberseite zu minimieren. Das Ausstechen und Aufnehmen dünner Chips von der Waferfolie ist ein kritischer Schritt, da die dünnen Chips sehr bruchempfindlich sind. Dieser Pickup-Prozess wurde für Chipgrößen mit bis zu 5mm x 5mm evaluiert und erfolgreich getestet.

Das Muster für den Klebstoffauftrag wurde optimiert, um ein kontrolliertes Fließen des Klebstoffs durch die Nutzung des Kapillareffekts und damit eine kontrollierte Benetzung am Chip zu erreichen. Der Klebstoff benetzt nicht über die Chipkanten zur Chipoberseite hinaus, so dass keine Klebstoffkontamination auf der Chipoberseite auftritt. Muster für medizinische Katheter-Anwendungen (s. Abb. 6) wurden erfolgreich mit 30µm dünnen Chips hergestellt. Diese wurden mit Hilfe des angepassten Chipbond-Verfahrens auf eine Polyimid-Folie bestückt, anschließend kontaktiert und eingebettet. Die Flexibilität des Aufbaus in Verbindung mit den dünnen platzsparenden Chips ermöglicht das Aufrollen und Einbringen z.B. in enge Katheter-Gehäuse.

Zusammenfassung

Abb. 6: Beispiel Chip mit 30µm DickeIm Rahmen dieses Artikels wurden verschiedene Möglichkeiten der manuellen und automatisierten Chipbestückung wie das Kleben, Vakuumlöten und Sintern bei Cicor, sowie deren besondere Herausforderungen und Einflussparameter kurz vorgestellt.

Abb. 6: Beispiel Chip mit 30µm DickeIm Rahmen dieses Artikels wurden verschiedene Möglichkeiten der manuellen und automatisierten Chipbestückung wie das Kleben, Vakuumlöten und Sintern bei Cicor, sowie deren besondere Herausforderungen und Einflussparameter kurz vorgestellt.

Gute Ergebnisse beim Chipbonden erfordern ein gut abgestimmtes Zusammenspiel wichtiger Kriterien. Die Materialqualität, Sauberkeit und Eignung für Chipbondprozesse, technische Parameter wie Bestückgenauigkeit, Kräfte, Temperaturen sowie die Auswahl der Verbindungsmaterialien und deren Auftrags-verfahren u.v.m spielen eine wichtige Rolle auch mit Blick auf die weitere Verarbeitung in nachfolgenden Prozessen zur el. Kontaktierung und Verkapselung der Chipaufbauten.

Zur erfolgreichen Verarbeitung optischer Chips sind z.B. bessere Reinraumklassen sowie gut geschulte und qualifizierte Mitarbeiter verfügbar. Unterschiedlichste Geometrien, z.B. sehr kleine oder sehr dünne Chips können heutzutage auch automatisiert bei Cicor in Radeberg verarbeitet werden, um vielfältige Anforderungen zur Miniaturisierung im Bereich Industrie, Medizintechnik sowie Luft- und Raumfahrt zu erfüllen. Dafür stehen eine Palette von sehr gut angepassten Prozessen und Anlagen für das Chipbonden zur Verfügung. Darüber hinaus werden immer wieder neue Materialien getestet und Prozessanpassungen erarbeitet, um erfolgreiche Lösungen für sich ständig ändernde Produkt- und Kundenanforderungen anbieten zu können.