Forschende am Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration in Berlin haben eine Integrationstechnologie entwickelt, um empfindliche elektronische Bauelemente mit einer biokompatiblen und weichen Verkapselung vor Umgebungseinflüssen zu schützen. In dem von der Europäischen Kommission geförderten ECSEL-Projekt ‚APPLAUSE' war eines der Ziele, ein flexibles und dehnbares Pflaster zu entwickeln, um die Vitalfunktionen von Herzpatient*innen zu messen.

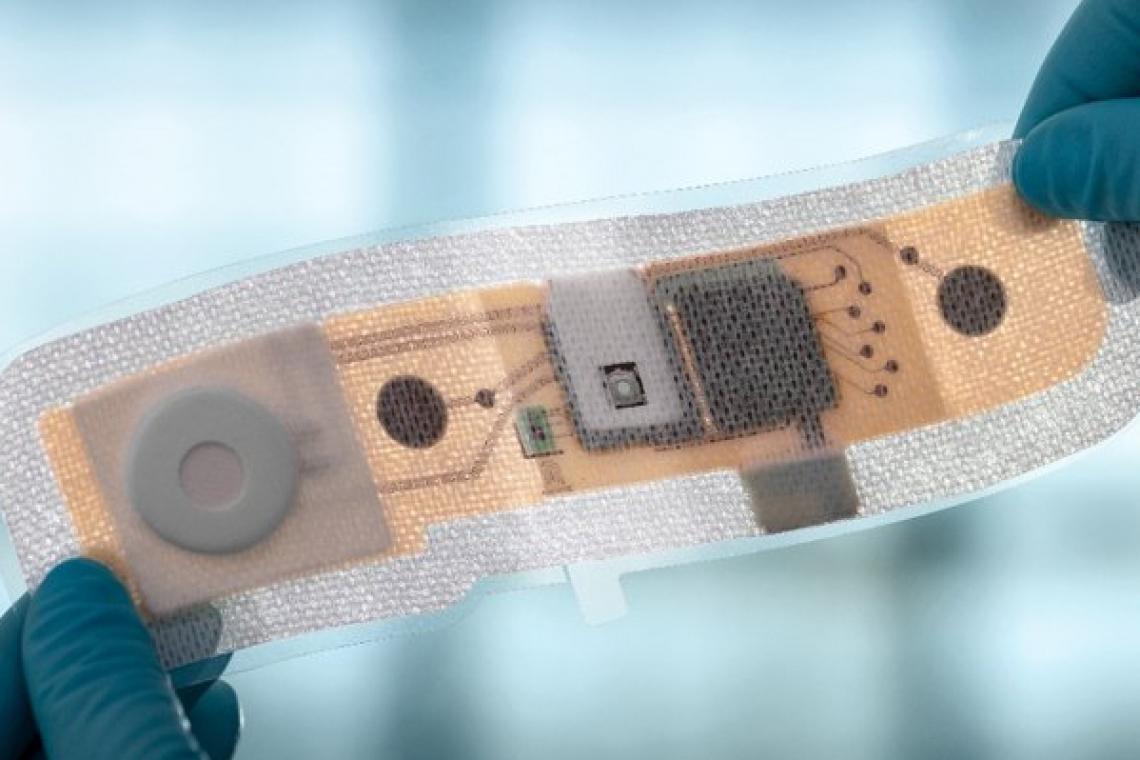

Researchers at the Fraunhofer Institute for Reliability and Microintegration in Berlin (IZM) have developed an integration technology to protect sensitive electronic components from environmental influences with a biocompatible and soft encapsulation. In the ECSEL project ‚APPLAUSE', funded by the European Commission, one of the goals was to develop a flexible and stretchable patch to measure the vital functions of heart patients.

Übergeordnetes Ziel des Projekts ‚APPLAUSE' war die Entwicklung kostengünstiger Fertigungs- und Integrationstechnologien für die Mikroelektronik – insbesondere die Optoelektronik – in Europa. Das entwickelte Pflaster-System enthält u. a. LEDs, System on Chips, Flash-Speicher und Beschleunigungssensoren. Die aufgenommenen und im System verarbeiteten Daten ermöglichen die kardiologische Überwachung mittels Photoplethysmogramm (PPG) sowie das Monitoring der Sauerstoffsättigung (SpO2), der Atmungsbewegung und der Bioimpedanz. Im Fokus der Forschenden des Fraunhofer IZM stand neben der System- und Schaltungsentwicklung die Aufbau- und Verbindungstechnik, bzw. die Integration eines dichtgepackten flexiblen Schaltungsträgers in das Pflaster. Dazu wurde ein Prozess entwickelt, der Dünnfilm-Technologien mit dehnbaren Substraten kombiniert, um komplexe Systeme für körpernahe Anwendungen zu realisieren.

Technologie und Parameterfindung

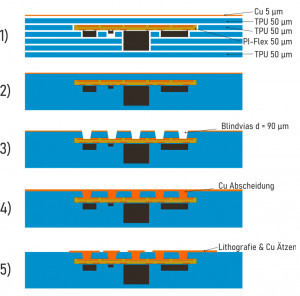

Abb. 2: Prozessablauf für die Dünnfilm-Flex-Integration in das TPU-SubstratAls Trägerfolie für das Pflaster wurde thermoplastisches Polyurethan (TPU) verwendet, das aufgrund seiner Flexibilität und Elastizität einen hohen Tragekomfort am Körper ermöglicht. Weiterhin lässt sich das Material kostengünstig und industriell mittels Leiterplattentechnologien verarbeiten (das verwendete Fertigungsformat war 610 mm x 457 mm).

Abb. 2: Prozessablauf für die Dünnfilm-Flex-Integration in das TPU-SubstratAls Trägerfolie für das Pflaster wurde thermoplastisches Polyurethan (TPU) verwendet, das aufgrund seiner Flexibilität und Elastizität einen hohen Tragekomfort am Körper ermöglicht. Weiterhin lässt sich das Material kostengünstig und industriell mittels Leiterplattentechnologien verarbeiten (das verwendete Fertigungsformat war 610 mm x 457 mm).

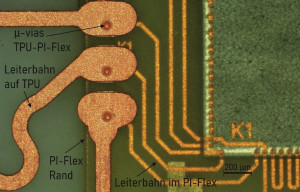

Zunächst wurde gezeigt, dass sich sehr dünne und dicht verdrahtete komplexe Flex-Schaltungen in einen TPU-Aufbau integrieren und elektrisch verbinden lassen. Die Dünnfilm-Flex-Schaltung auf Basis von Polyimid mit Abmessungen 12 mm x 9 mm hatte eine Gesamtdicke von 50 µm, enthielt als eingebettete Komponenten je zwei 20 µm dicke Testchips (mit Daisy-Chain-Strukturen und Cu-Kontakten) und wurde von der Abteilung Wafer-Level-System-Integration am Fraunhofer IZM (Kai Zoschke) entwickelt und zur Verfügung gestellt. Mit dem Testaufbau sollte die maximal mögliche Verdrahtungsdichte im Inneren des PI-Flexes und die Verbindungsdichte auf das TPU-Substrat untersucht werden. Die Anordnung im Daisy-Chain-Format ermöglichte die Untersuchung und den Test des Gesamtsystems über die Fan-out Strukturen im TPU-Teil inklusive der Strukturen des eingebetteten PI-Flexes im Inneren.

Vor der Einbettung des PI-Flexes wurden zunächst transparente TPU-Folien mittels UV-Laser strukturiert zugeschnitten. Über eine Verstiftung wurden die TPU-Einzelfolien, die Flex-Schaltung und eine 5 µm dünne Cu-Folie mechanisch stabil zueinander ausgerichtet. Die anschließende Lamination erfolgte in einer Kurztaktpresse bei 165 °C und einem Druck von 10 bar (siehe Abb. 2). Dank vorab implementierter Erkennungsmarken im Layout konnten anschließend µ-vias (Durchmesser 90 µm) zur Kontaktierung der Fan-out Strukturen im TPU und der Kontaktpads im PI-Flex mittels eines UV-Lasers gesetzt werden. Die Herausforderung war hier geeignete Parameter zu finden, um die Kupferfläche der Kontakte freizulegen, ca. 50 µm tief durch TPU zu bohren und auf den nur 10 µm dünnen Cu-Pads der Flex-Schaltung zu stoppen.

Die elektrische Kontaktierung erfolgte durch galvanische Kupferabscheidung in die µ-vias. Leiterzüge und Messkontakte wurden im letzten Schritt mittels Photolithographie und Ätzen definiert. (Abb. 3).

Abb. 5: Angepasster Prozessablauf mit unterschiedlichen BauelementenDie Substrate wurden während des Durchlaufens der gesamten Prozesskette mittels optischer und elektrischer Messungen charakterisiert. Die Prozessparameter für das Laminieren wurden dahingehend optimiert, dass keiner der eingebetteten Si-Chips in der optischen Inspektion Brüche aufwies. Die elektrische Prüfung von zwölf Aufbauten zeigten geringe Kontaktwiderstände und vollständig durchgängige Daisy-Chains. Im Gesamtergebnis waren alle Strukturen kontaktiert, d. h. alle Mikrovias zwischen TPU-Substrat und dem PI-Dünnfilm-Flex waren funktional. Elektrische Messungen, die nach abschließenden Zuverlässigkeitsuntersuchungen (200 h bei 85 °C und 85 % Luftfeuchte) durchgeführt wurden, ergaben, dass keine ausgeprägten Abweichungen zu den initialen Messwerten auftraten.

Abb. 5: Angepasster Prozessablauf mit unterschiedlichen BauelementenDie Substrate wurden während des Durchlaufens der gesamten Prozesskette mittels optischer und elektrischer Messungen charakterisiert. Die Prozessparameter für das Laminieren wurden dahingehend optimiert, dass keiner der eingebetteten Si-Chips in der optischen Inspektion Brüche aufwies. Die elektrische Prüfung von zwölf Aufbauten zeigten geringe Kontaktwiderstände und vollständig durchgängige Daisy-Chains. Im Gesamtergebnis waren alle Strukturen kontaktiert, d. h. alle Mikrovias zwischen TPU-Substrat und dem PI-Dünnfilm-Flex waren funktional. Elektrische Messungen, die nach abschließenden Zuverlässigkeitsuntersuchungen (200 h bei 85 °C und 85 % Luftfeuchte) durchgeführt wurden, ergaben, dass keine ausgeprägten Abweichungen zu den initialen Messwerten auftraten.

Aufbau TPU-Modul

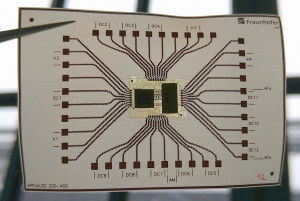

Basierend auf den Ergebnissen der Entwicklungsphase wurde ein funktionsfähiges System erstellt. Dies bedeutet, dass ein Mess- und Auswertemodul, das in der Dünnfilm-Flex-Technologie hergestellt wurde, in TPU verkapselt wurde, um es vor mechanischen und Umwelteinflüssen zu schützen. Der funktionale Schaltungsträger bestand aus einem dreilagigen Polyimid-Dünnfilm-Flex mit einer Dicke von 50 µm. Die verwendeten Bauelemente waren vielfältiger und in größerer Anzahl als im Testaufbau, wiesen jedoch auch erhebliche Höhenunterschiede auf, die von 50 µm (ICs) bis zu 1 mm (handelsübliche SMD-Komponenten) reichten. Daher war es erforderlich, einige Prozessparameter anzupassen. Insbesondere für das Laminieren wurden mehrere individuell zugeschnittene TPU-Folien im Pressstapel verwendet, um sowohl die Höhenunterschiede auszugleichen als auch einen gleichmäßigen Materialfluss des TPUs während des Schmelzvorgangs sicherzustellen. Da das Messmodul mehrere Signalausgänge hatte, war eine weitere Herausforderung, die Mikrovias präzise auf die Kontakte zu setzen.

Da das Modul auf das eigentliche Pflastersubstrat gelötet werden sollte, wurden die nach außen führenden Kontakte im nasschemischen Bad versilbert. Nach Abschluss der Prozesse wurde das Modul per Laser entsprechend der Kontur vereinzelt.

Aufbau TPU-Pflaster und Montage

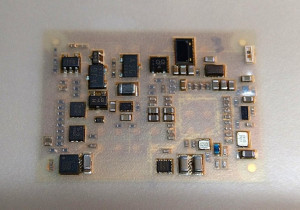

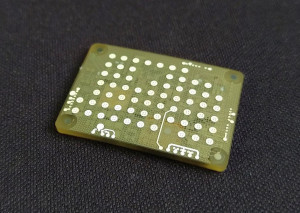

Für die Entwicklung der Integration in das Pflaster, wurde ein Testlayout entwickelt um das Löten des TPU-Moduls sowie weiterer SMD-Komponenten zu untersuchen. Das Layout beinhaltet Kupfer-Elektroden (ohne Silberchloridbeschichtung) und verfügt teilweise über mäandrierte Leiterbahnen, um die Dehnbarkeit der Leiterzüge unter Zugspannung zu gewährleisten. Zur Herstellung der Trägerfolie des Pflaster-Demonstrators wurde die gleiche 100 µm TPU-Folie, wie beim oben beschriebenen Testmodul verwendet. Die einlagige Verdrahtungslage bestand aus 5 µm dickem Kupfer. Der Lötstopplack wurde anders als bei konventionellen Leiterplatten jedoch nur lokal um die Kontaktflächen aufgebracht, damit der flexible / elastische Charakter der Polyurethan-Folie in der Fläche des Pflasters erhalten bleibt. Die Kupferstrukturen wurden abschließend stromlos versilbert, mit den Testkomponenten (SMD, TPU-Modul und Schalter) bestückt und im Reflow-Ofen bei 162 °C mit SnBi-Lot aufgelötet. Schließlich wurden die Demonstratoren mit einem Laser vereinzelt.

Abb. 9: Selektiver Lötstopplack auf Pflaster-Demonstrator

Abb. 9: Selektiver Lötstopplack auf Pflaster-Demonstrator

Abb. 10.: Pflaster-Demonstrator mit gelötetem TPU-Modul und SMD-Komponenten

Abb. 10.: Pflaster-Demonstrator mit gelötetem TPU-Modul und SMD-Komponenten

Fazit

Es konnte erfolgreich gezeigt werden, dass eine robuste und zuverlässige TPU-Verkapselung dünner (Polyimid-) Schaltungsträger möglich ist. Mittels gängiger Leiterplattenprozesse ist die TPU-Einbettung von in Polyimid integrierten, ultradünnen Chips sowie oberflächenbestückten SMD-Komponenten realisierbar. Die Funktionalität der Schaltung wird durch die Prozessierung oder das Material nicht beeinträchtigt und mit der Verkapselung erhalten die Komponenten den notwendigen Schutz vor Umgebungs- und Stresseinflüssen, die sich aus dem Anwendungsszenario ergeben. Das TPU-Package kann mit SnBi-Lot auf Schaltungsträger gelötet werden. Alternativ wäre bei großzügig dimensionierten Kupferstrukturen- und Abständen auch eine elektrisch leitfähige Klebung möglich. Für die Anwendung wird das Pflaster ergänzend mit gedruckten Elektrodenoberflächen sowie hautfreundlichem Adhäsionsfolien versehen, um den Tragekomfort zu erhöhen. Denkbar wäre auch ein zweilagiges TPU-Substrat (mit Vias), falls die Schaltungsauslegung dies erfordert oder um die Packungsdichte zu erhöhen. Als weitere Optimierung wäre eine textile Oberfläche vorstellbar, die vorab auf die TPU-Folie des Pflasters laminiert werden könnte.

Bildquellen

Fraunhofer IZM

Referenzen

[1] L. Boettcher; D. Manessis; A. Ostmann; S. Karaszkiewicz; H. Reichl: Embedding of Chips for System in Package realization - Technology and Applications, 2008 3rd International Microsystems, Packaging, Assembly & Circuits Technology Conference, 2008, 383–386, doi: 10.1109/IMPACT.2008.4783892

[2] N. Islam; K.H. Tan; S.W. Yoon; T. Chen: High Density Ultra-Thin Organic Substrates for Advanced Flip Chip Packages, 69th Electronic Components & Technology Conference, Las Vegas, USA, May 28th–May 31st, 2019

[3] J.P.L. Leenen; C. Leerentveld; J.D. van Dijk; H.L. van Westreenen; L. Schoonhoven; G.A. Patijn: Current Evidence for Continuous Vital Signs Monitoring by Wearable Wireless Devices in Hospitalized Adults: Systematic Review, Journal of Medical Internet Research, 2020 Jun 17;22(6): e18636, doi: 10.2196/18636, PMID: 32469323; PMCID: PMC7351263